AI CERTS

2 months ago

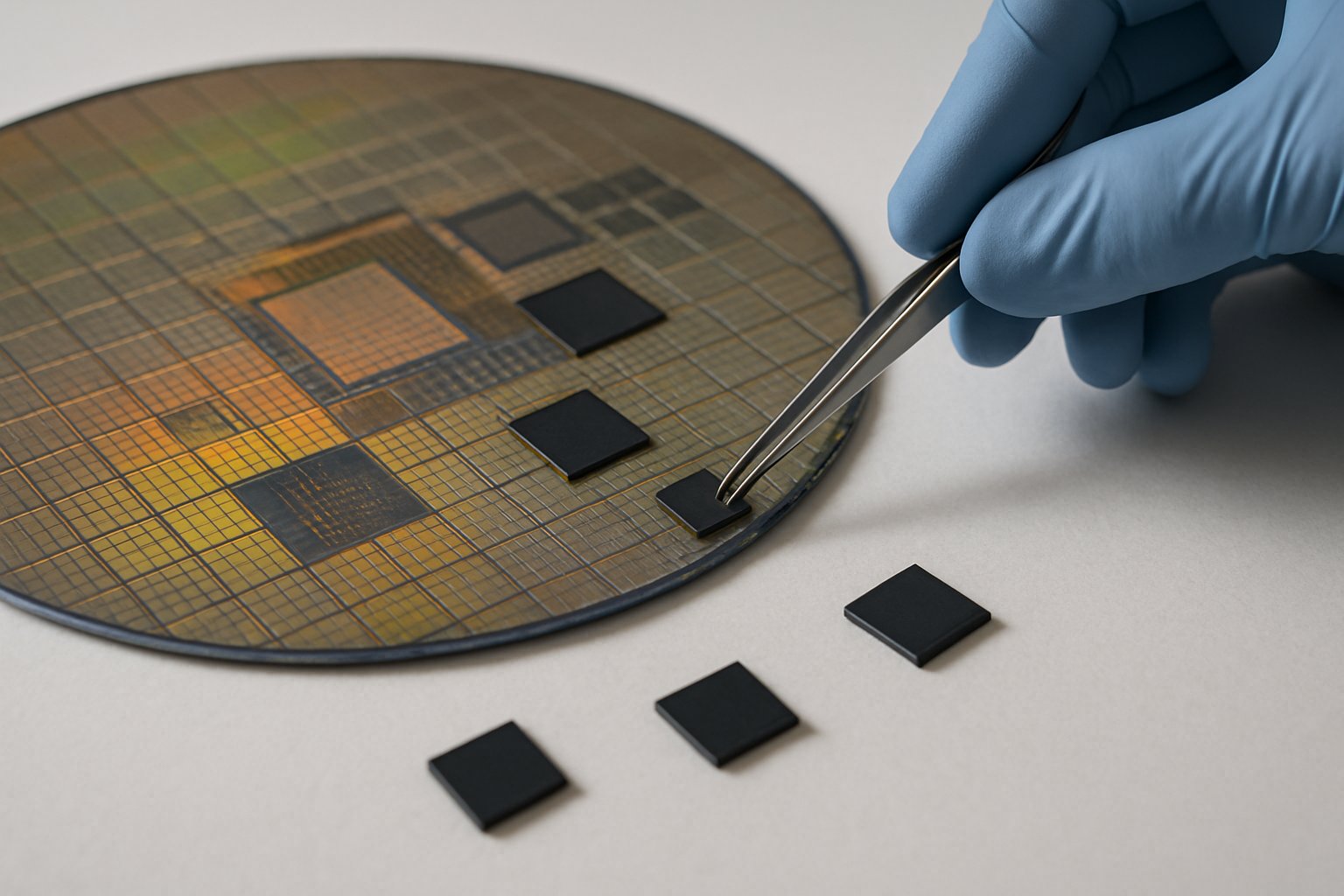

Cognichip’s $60M Bet on AI Chip Design

However, questions about production evidence remain. This article unpacks the raise, the technology, and what comes next for AI-driven silicon creation.

Funding Signals Market Shift

Cognichip’s fresh funding arrives less than a year after its $33 million seed. Therefore, the company almost tripled available capital during turbulent venture markets. Furthermore, the oversubscribed round attracted SBI Investment alongside semiconductor insiders. In contrast, rival AI-EDA startups closed smaller amounts this quarter. Analysts say the larger ticket size validates AI Chip Design as a strategic frontier. Nevertheless, valuation details were not disclosed, leaving observers to estimate implied momentum.

The round matters because EDA remains a $10-15 billion niche dominated by three incumbents. Consequently, outsized checks can attract mid-market customers hungry for alternatives. Cognichip must now convert capital into proof. These financial signals stress urgency while underscoring competitive pressure. However, sustainable advantage still hinges on execution.

Funding strength highlights investor confidence. Yet evidence of shipped silicon is still pending, creating pressure for timely milestones.

How ACI Model Works

At the core sits Cognichip’s Artificial Chip Intelligence, or ACI®. The physics-informed foundation model embeds manufacturing constraints directly into learning loops. Additionally, the model spans planning, placement, and verification tasks inside a unified workflow. Therefore, engineers can explore design spaces quickly while respecting foundry rules.

ACI leverages large context windows to ingest RTL, layout data, and process design kits. Subsequently, the system proposes floor-plans and routing strategies that traditional tools evaluate later. Meanwhile, reinforcement signals tune objectives such as power, performance, and area. Experts label this closed-loop orchestration the primary differentiator within modern AI Chip Design stacks.

Core technical pillars:

- Physics constraints guide generative search, limiting impractical layouts.

- Synthetic data augments scarce proprietary datasets, improving generalization.

- Secure on-prem deployments protect customer IP during model fine-tuning.

These features create a compelling narrative. However, verification remains the long pole, and public whitepapers are scarce. The architecture promises speed, yet real silicon will prove true capability.

Promised Efficiency Metrics Explained

Cognichip advertises dramatic improvements. Company material cites up to 75 percent development reduction cost and 50 percent shorter design timeline. Furthermore, the startup claims engagement with more than 30 semiconductor firms. Consequently, potential customers envision faster iterations and decreased budget risk.

Industry veterans find the numbers attractive. Nevertheless, no independent audit confirms them. Verification labs still need to sign off proposed layouts, and foundries must validate manufacturability. In contrast, incumbent EDA suites possess decades of silicon-proven pedigree. Therefore, analysts urge caution until tape-outs surface.

Key metric takeaways appear below:

- Reduction cost: asserted 75 percent, not yet validated.

- Timeline: marketed 50 percent faster, awaiting production proof.

- Return on investment: theoretical, contingent on risk tolerance.

These headline gains excite stakeholders. However, real-world projects must close the evidence gap before widespread adoption follows.

Competitive Landscape And Risks

Synopsys, Cadence, and Siemens EDA already integrate machine learning assistants. Moreover, each incumbent commands entrenched workflows, sales channels, and verification sign-off credibility. Consequently, Cognichip faces formidable brand inertia. Additionally, rival startups ChipAgents and Ricursive recently announced new products, intensifying the race.

Several structural risks persist. Firstly, access to proprietary design data remains difficult. Secondly, incumbent vendors may bundle advanced AI modules at minimal incremental cost, neutralizing pricing leverage. Thirdly, production tape-outs carry high failure penalties if verification gaps surface. Therefore, early enterprise pilots represent both an opportunity and hazard.

Competitive pressure accelerates innovation. Yet risks demand transparent benchmarks and cooperative foundry partnerships to build trust.

Adoption Hurdles And Evidence

Prospective users ask three questions. Will ACI integrate smoothly with existing flows? Can intellectual property remain secure? Will verification pass without manual rework? Subsequently, Cognichip markets flexible APIs and on-prem safeguards to address concerns. Nevertheless, public case studies remain under wraps.

Meanwhile, the company notes ongoing projects with unnamed customers. However, journalists confirm no completed tape-out solely designed by ACI. Consequently, observers monitor the timeline closely. Moreover, investors joining the board may provide leverage to secure marquee pilots.

These hurdles underscore the importance of transparent milestones. Consequently, upcoming quarters will reveal whether promises translate into silicon.

Takeaways For Industry Leaders

Engineering executives must track AI Chip Design momentum. Furthermore, they should evaluate vendor roadmaps, assess risk, and model potential reduction cost benefits. In contrast, ignoring progress could surrender strategic advantage to faster competitors. Therefore, pilot engagements using non-critical blocks may balance experimentation with safety.

Professionals seeking deeper expertise can pursue the AI-Product Manager™ certification. Consequently, leaders gain structured frameworks for deploying advanced design intelligence across teams.

The industry stands at an inflection point. However, disciplined experimentation and talent development will decide winners.

These insights prepare organizations for informed decisions. Meanwhile, upcoming customer announcements may redefine competitive baselines.

Next Steps For Professionals

Monitor funding disclosures, roadmap updates, and independent benchmarks. Additionally, allocate budget for exploratory projects that validate claimed timeline acceleration. Moreover, integrate cross-functional reviews to address security and compliance.

Consequently, firms that learn fastest will capture market share when AI-native flows mature. Nevertheless, patience remains necessary because silicon success cycles span years.

Proactive learning and measured pilots establish readiness. Therefore, strategic diligence now will pay dividends during the next design cycle.

The outlined actions position stakeholders for purposeful engagement. In contrast, passive observation risks obsolescence as automation advances.

Conclusion And Outlook

Cognichip’s $60 million raise spotlights accelerating interest in AI Chip Design. Moreover, promised 75 percent reduction cost and 50 percent faster timeline could democratize custom silicon. However, absence of verified tape-outs means scrutiny remains high. Consequently, investors, engineers, and competitors will watch upcoming quarters for concrete proof.

Industry leaders should evaluate pilots, build internal literacy, and develop governance for AI-driven workflows. Meanwhile, certifications like the linked program empower professionals to navigate emerging complexities. Therefore, seize this moment to position teams at the forefront of semiconductor innovation.

Disclaimer: Some content may be AI-generated or assisted and is provided ‘as is’ for informational purposes only, without warranties of accuracy or completeness, and does not imply endorsement or affiliation.