AI CERTS

2 months ago

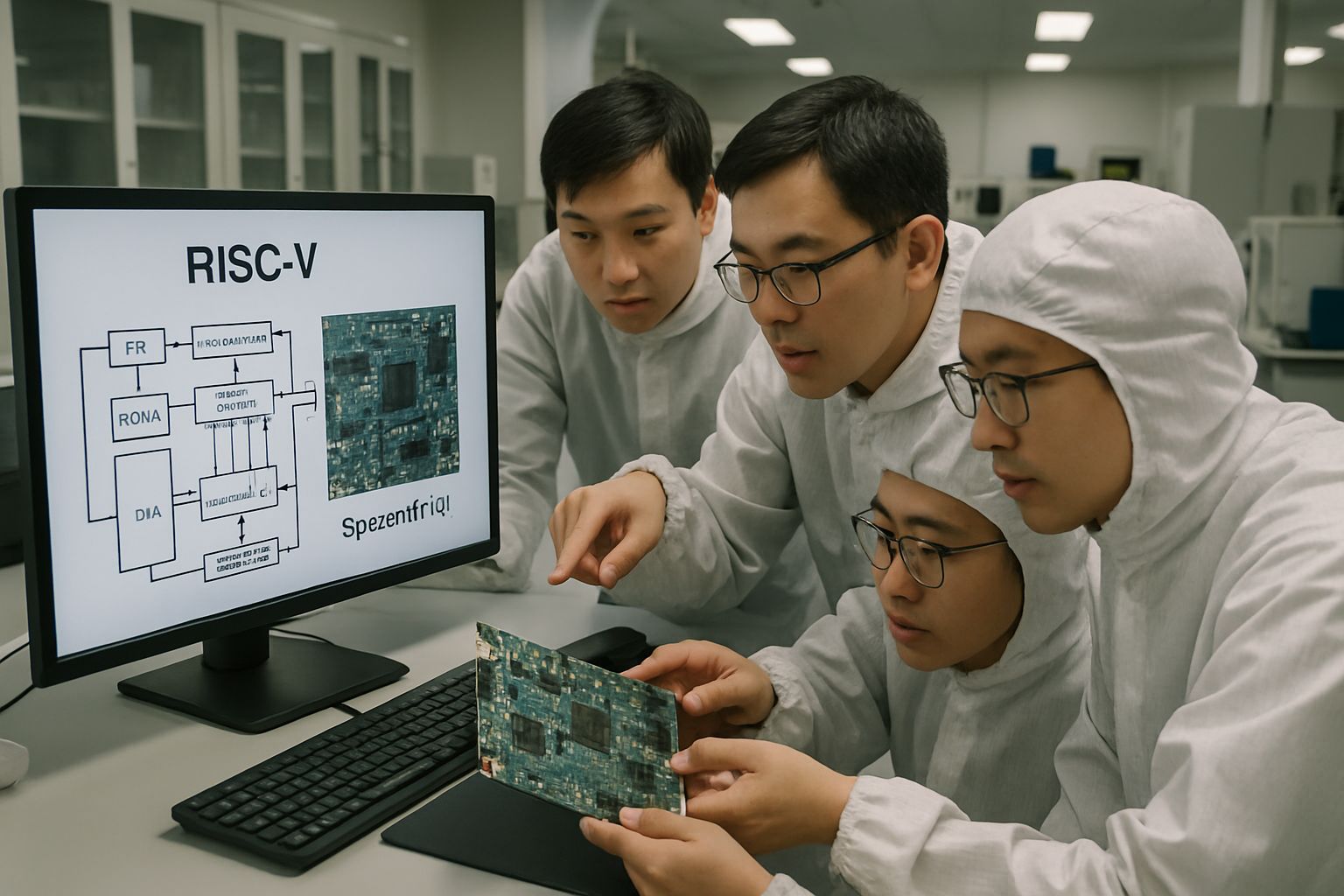

China Bets Big on RISC-V Architecture with SpacemiT K3 Launch

The launch signals China’s accelerating pivot from microcontroller projects toward performance cores that challenge x86 and Arm incumbents. This article unpacks the product, places it inside the wider Chinese timeline, and examines broader implications for Open-Source hardware. Furthermore, we contrast competing domestic designs, survey market forecasts, and outline policy pressures shaping future deployments. Finally, professionals receive guidance on skills and certifications that can solidify their position in this fast-growing arena.

China's Growing RISC-V Momentum

Historically, Chinese groups embraced the RISC-V Architecture for microcontrollers powering IoT sensors and student projects. However, funding rounds, policy incentives, and talent shifts have moved the focus toward high-performance implementations. Alibaba’s DAMO Academy, CAS’s XiangShan team, and startups like RIVAI all taped out multi-core chips during 2025.

Consequently, analysts at Omdia estimate RISC-V shipments will climb roughly 50 percent every year until 2030. That trajectory could place open designs at nearly one-quarter global share by decade’s end, according to their 17 billion-unit model.

These numbers illustrate swelling domestic ambition. Therefore, understanding flagship launches like SpacemiT K3 becomes essential for tech planners.

Momentum is unmistakable across academia and industry. Next, we dissect SpacemiT’s latest silicon to see where it fits.

Inside SpacemiT K3 Chip

SpacemiT K3 targets edge servers and smart terminals that must balance general code with machine-learning tasks. Moreover, company claims list eight X100 cores at 2.4 GHz plus a matrix engine delivering 60 TOPS. Additionally, support for RVV and FP8 promises efficient low-precision inference on transformer workloads.

Engineers will find dual 32 GB LPDDR5 channels and a 15–25 W thermal envelope, making the board suitable for fanless enclosures. Meanwhile, the design follows the RVA23 profile that standardizes privilege, vector, and debug extensions for upper-range client devices.

- Company positions K3 as a single-chip AI CPU for 30–80 billion parameter models.

- SpacemiT K3 supports the RISC-V Architecture plus custom vector extensions.

- RVA23 compliance eases porting of existing RISC-V toolchains and operating systems.

Collectively, these specs push Chinese silicon deeper into mid-range AI workloads. However, rivals have also unveiled ambitious cores, warranting comparison.

Comparing Emerging Chinese Designs

Alibaba’s C930 server core, shipped in March 2025, scales to 128 threads and targets cloud inference clusters. Similarly, RIVAI’s Lingyu processor and CAS’s XiangShan project chase higher compute density through chiplet approaches. Nevertheless, SpacemiT K3 differentiates itself by focusing on 15–25 W envelopes that suit edge boxes rather than racks.

In contrast, the C930 advertises 5 GHz peak speeds but demands far larger cooling budgets. Consequently, Chinese OEMs may allocate K3 to retail robots, industrial gateways, and vehicle infotainment systems.

The shared adoption of the RISC-V Architecture simplifies cross-platform firmware work, yet performance profiles differ sharply. Engineers must therefore benchmark kernels under real thermal limits before final platform selection.

Each design fills a distinct power-performance niche. Next, we examine whether forecasts justify such parallel bets.

Market Forecasts And Projections

Omdia predicts annual RISC-V unit growth near 50 percent through 2030, reaching 17 billion shipments. Moreover, some models assign the RISC-V Architecture up to 25 percent market share by that horizon.

Analysts tie expansion to automotive ECUs, industrial controllers, and energy-efficient edge AI products entering mass production. Additionally, growing university adoption supplies a fresh workforce fluent in modern toolchains.

- Low licensing costs accelerate vendor experimentation.

- RVA23 profile promotes software portability across devices.

- Open-Source communities shorten debug and security review cycles.

Consequently, supply chain analysts forecast broader foundry support for 12 nm and below nodes. Projections appear bullish yet contingent on robust software layers. Therefore, geopolitical tensions could still reshape adoption curves.

Geopolitics And Policy Tensions

Washington policymakers debate restricting collaboration on open standards, fearing unintended technology transfer. However, the CSIS report from April 2025 advises engagement, noting the governance body sits in neutral Switzerland.

In China, officials view the RISC-V Architecture as a sovereignty hedge that reduces Arm and x86 dependence. Moreover, funding programs at provincial levels subsidize tape-outs and verification tools for startups.

Nevertheless, export controls on advanced EDA software and extreme-ultraviolet lithography still limit cutting-edge ambitions. Consequently, many Chinese RISC-V projects tape out on 14 nm or older processes, sacrificing top efficiency.

Tensions create both urgency and uncertainty for chip planners. Next, we address technical and ecosystem hurdles confronting Open-Source hardware teams.

Challenges For Open-Source Hardware

Despite progress, software maturity challenges the RISC-V Architecture in enterprise workloads. Developers still port many commercial libraries from x86 or Arm, creating latency for production deployments. Additionally, verification of complex cache controllers or coherent interconnects demands costly simulation farms.

Open-Source licensing also invites nuanced intellectual-property disputes at the microarchitecture level. In contrast, proprietary ISAs bundle indemnification that some OEMs still value.

- Advanced node access depends on geopolitical approvals.

- Benchmarks lack third-party verification for many RVA23 devices.

- Toolchain fragmentation slows commercial testing.

These challenges highlight critical gaps. However, targeted education and certification programs can ease adoption.

Skills Pathways And Certification

Engineering leaders need teams versed in the RISC-V Architecture vector compilers, board bring-up, and security hardening. Consequently, companies increasingly request proof of formal training when hiring RISC-V specialists.

Professionals can enhance their expertise with the AI Engineer™ certification. Moreover, the syllabus covers assembly fundamentals, RVA23 compliance, and deployment of modern Chinese reference boards.

Therefore, enterprises gain shorter onboarding cycles and reduced integration risk. Skills investment converts ecosystem hype into operational readiness.

Chinese innovators are scaling the RISC-V Architecture beyond hobby boards, with SpacemiT K3 illustrating the edge-AI frontier. Market forecasts remain bullish for the RISC-V Architecture, yet geopolitical and ecosystem challenges demand disciplined engineering strategies. Consequently, leaders who leverage certifications, evaluate RVA23 platforms, and benchmark Open-Source designs will capture early advantage. Act now to build skills and partnerships while the opportunity window stays wide.